SPI(Serial Peripheral Interface,串行外设接口)是Motorola公司提出的一种同步串行数据传输标准,是一种高速的,全双工,同步的通信总线,在很多器件中被广泛应用。

SPI相关缩写

SS: Slave Select,选中从设备,片选。

CKPOL (Clock Polarity) = CPOL = POL = Polarity = (时钟)极性

CKPHA (Clock Phase) = CPHA = PHA = Phase = (时钟)相位

SCK = SCLK = SCL = SPI的时钟(Serial Clock)

Edge = 边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿(falling edge)。

对于一个时钟周期内,有两个edge,分别称为:

Leading edge = 前一个边沿 = 第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;

Trailing edge = 后一个边沿 = 第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;

接口

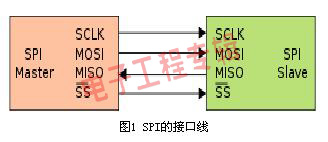

SPI接口经常被称为4线串行总线,以主/从方式工作,数据传输过程由主机初始化。

如图1所示,其使用的4条信号线分别为:

1) SCLK:串行时钟,用来同步数据传输,由主机输出;

2) MOSI:主机输出从机输入(Master Output Slaver Input)数据线;

3) MISO:主机输入从机输出数据线;

4) SS:片选线,低电平有效,由主机输出

在SPI总线上,某一时刻可以出现多个从机,但只能存在一个主机,主机通过片选线来确定要通信的从机。这就要求从机的MISO口具有三态特性,使得该口线在器件未被选通时表现为高阻抗。

SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash,ADC等的Slaver SPI进行通讯。而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。

数据传输

在一个SPI时钟周期内,会完成如下操作:

1) 主机通过MOSI线发送1位数据,从机通过该线读取这1位数据;

2) 从机通过MISO线发送1位数据,主机通过该线读取这1位数据。

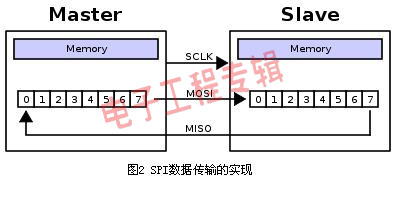

这是通过移位来寄存器实现的。如图2所示,主机和从机各有一个移位寄存器,且二者连接成环。随着时钟脉冲,数据按照从高位到低位的方式依次移出主机寄存器和从机寄存器,并且依次移入从机寄存器和主机寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

时钟极性和时钟相位

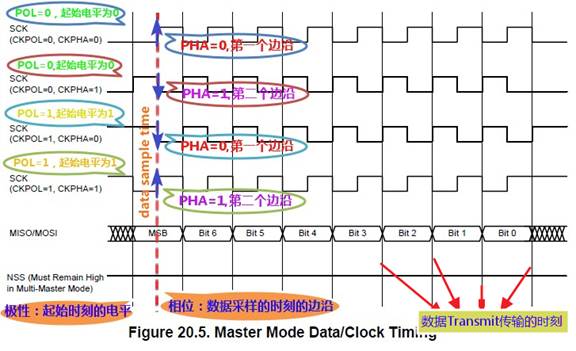

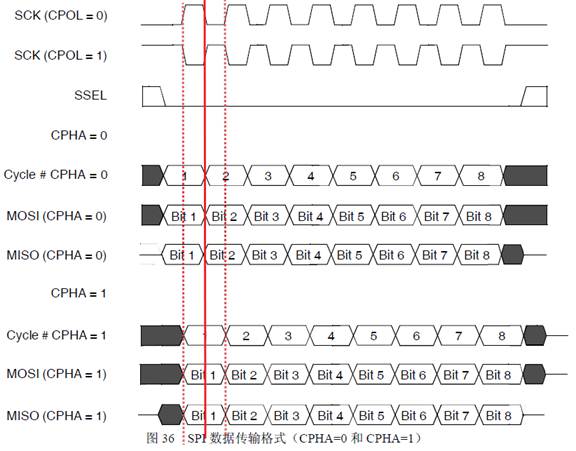

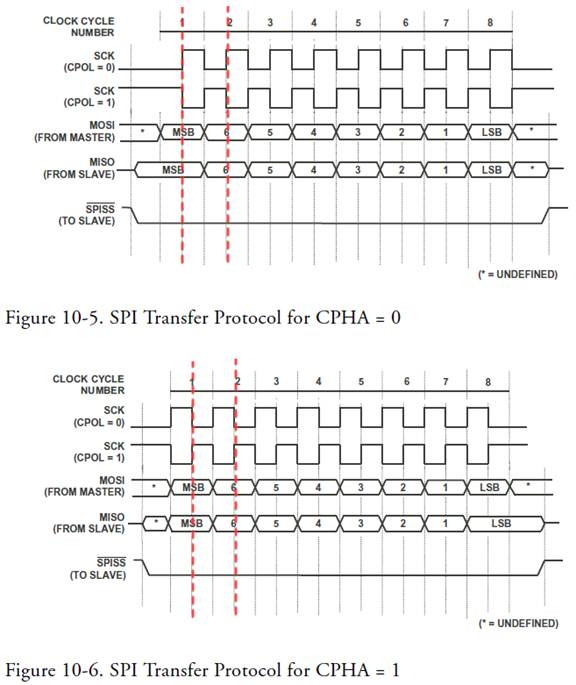

在SPI操作中,最重要的两项设置就是时钟极性(CPOL或UCCKPL)和时钟相位(CPHA或UCCKPH)。时钟极性设置时钟空闲时的电平,时钟相位设置读取数据和发送数据的时钟沿。

主机和从机的发送数据是同时完成的,两者的接收数据也是同时完成的。所以为了保证主从机正确通信,应使得它们的SPI具有相同的时钟极性和时钟相位。

CPOL极性

先说什么是SCLK时钟的空闲时刻,其就是当SCLK在发送8个bit比特数据之前和之后的状态,与此对应的,SCLK在发送数据的时候,就是正常的工作的时候,有效active的时刻了。

先说英文,其精简解释为:Clock Polarity = IDLE state of SCK。

再用中文详解:

SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1:

CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high;

CPOL=1,时钟空闲idle时候的电平是高电平,所以当SCLK有效的时候,就是低电平,就是所谓的active-low;

CPHA相位

首先说明一点,capture strobe = latch = read = sample,都是表示数据采样,数据有效的时刻。

相位,对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,0对应着第一个边沿,1对应着第二个边沿。

CPOL=0:

对于CPHA=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿;

对于CPHA=1,idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿;

CPOL=1:

对于CPHA=0,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;

对于CPHA=1,idle时候的是高电平,第二个边沿就是从低变到高,所以是上升沿;

用图文形式表示,更加容易看懂:

CKP和CKE

CKP和CKE是Microchip的PIC系列芯片中的说法。

(1)CKP是Clock Polarity Select,就是极性=CPOL:

CKP,虽然名字和CPOL不一样,但是都是指时钟极性的选择,定义也一样:

CKP: Clock Polarity Select bit

1 = Idle state for clock (CK) is a high level

0 = Idle state for clock (CK) is a low level

所以不多解释。

(2)CKE是Clock Edge Select,就是相位=CPHA:

CKE: SPI Clock Edge Select bit

1 = Transmit occurs on transition from active to Idle clock state

0 = Transmit occurs on transition from Idle to active clock state

意思是:

1 =(数据)传输发生在时钟从有效状态转到空闲状态的那一时刻

0 =(数据)传输发生在时钟从空闲状态转到有效状态的那一时刻

其中,数据传输的时刻,即上图中标出的“数据transmit传输的时刻”。

CKE的定义也跟CPHA相同。

所以,CKP和CKE所对应的取值的含义为:

When CKP = 0:

CKE=0 => Data transmitted on rising edge of SCK(idle时候是低电平,从空闲到有效,就是从低电平到高电平,所以是上升沿)

CKE=1 => Data transmitted on falling edge of SCK(idle时候是低电平,从有效到空闲,就是从高电平到低电平,所以是下降沿)

When CKP = 1:

CKE=0 => Data transmitted on falling edge of SCK(idle时候是高电平,从空闲到有效,就是从高电平到低电平,所以是下降沿)

CKE=1 => Data transmitted on rising edge of SCK(idle时候是高电平,从有效到空闲,就是从低电平到高电平,所以是上升沿)

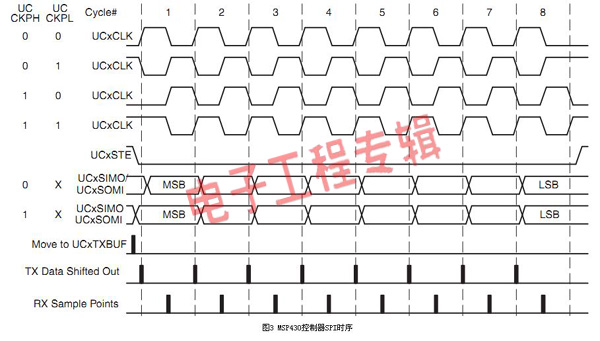

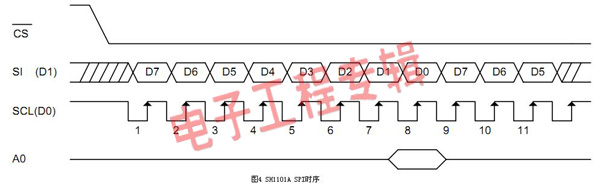

举例来说,分别选取MSP430控制器和OLED驱动SH1101A为主从机,图3和图4为它们的SPI时序。由图4可知,SH1101A的SPI时钟空闲时为高电平,并且在后时钟沿接收数据(后时钟沿在数据的中间部位),则MSP430控制器SPI的设置应与此保持一致。从图3中可以看出,要使得时钟在空闲时为高电平,应将UCCKPL置1;要使得在后时钟沿接收数据,应将UCCKPH清零。

下面再列出其他一些地方找到的,常见的SPI的四种模式的时序图,供参考:

如何看懂和记忆CPOL和CPHA

所以,关于在其他地方介绍的,看似多么复杂难懂难记忆的CPOL和CPHA,其实经过上面解释,就肯容易看懂了:

去看时序图,如果时钟SCLK的起始电平是0,那么CPOL=0,如果是1,那么CPOL=1。

然后看数据采样时刻,即时序图数据线上的数据矩形区域的中间所对应的位置,对应到上面SCLK时钟的位置,对应着是第一个边沿或是第二个边沿,即CPHA是0或1。(对应的是上升沿还是下降沿,要根据对应的CPOL的值,才能确定)。

即:

(1)如何判断CPOL:SCLK的空闲时候电压是0还是1,决定了CPOL是0还是1;

(2)如何判断CPHA:而数据采样时刻对应着的SCLK的电平,是第一个边沿还是第二个边沿,对应着CPHA为0还是1。

软件中如何设置SPI的极性和相位

SPI分主设备和从设备,两者通过SPI协议通讯。

设置SPI的模式,是从设备的模式,决定了主设备的模式。

所以要先去搞懂从设备的SPI是何种模式,然后再将主设备的SPI的模式,设置和从设备相同的模式,即可正常通讯。

对于从设备的SPI是什么模式,有两种:

(1)固定的,设备硬件决定的。

SPI从设备,具体是什么模式,相关的datasheet中会有描述,需要自己去datasheet中找到相关的描述,即:

关于SPI从设备,在空闲的时候,是高电平还是低电平,即决定了CPOL是0还是1;

然后再找到关于设备是在上升沿还是下降沿去采样数据,这样就是,在定了CPOL的值的前提下,对应着可以推算出CPHA是0还是1了。

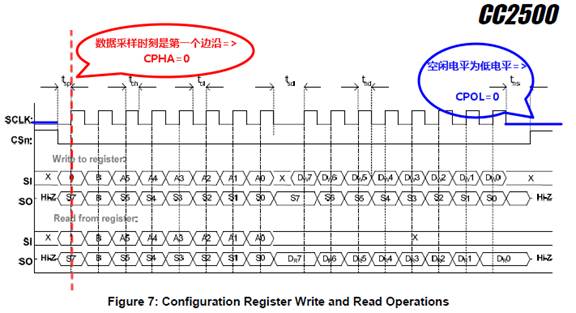

举例1:

CC2500 - Low-Cost Low-Power 2.4 GHz RF Transceiver的datasheet中SPI的时序图是:

从图中可以看到,最开始的SCLK和结束时候的SCLK,即空闲时刻的SCLK,是低电平,推导出CPOL=0,然后可以看到数据采样的时候,即数据最中间的那一点,对应的是SCLK的第一个边沿,所以CPHA=0(此时对应的是上升沿)。

举例2:

SSD1289 - 240 RGB x 320 TFT LCD Controller Driver的datasheet中提到:

“SDI is shifted into 8-bit shift register on everyrising edge of SCK in the order of data bit 7, data bit 6 …… data bit 0.”

意思是,数据是在上升沿采样,所以可以断定是CPOL=0,CPHA=0,或者CPOL=1,CPHA=1的模式,但是至于是哪种模式。

按理来说,接下来应该再去确定SCLK空闲时候是高电平还是低电平,用以确定CPOL是0还是1,但是datasheet中没有提到这点。

所以,此处,目前不太确定,是两种模式都支持,还是需要额外找证据却确定CPOL是0还是1.

(2)可配置的,由软件自己设定

从设备也是一个SPI控制器,4种模式都支持,此时只要自己设置为某种模式即可。

然后知道了从设备的模式后,再去将SPI主设备的模式,设置为和从设备模式一样,即可。

对于如何配置SPI的CPOL和CPHA的话,不多细说,多数都是直接去写对应的SPI控制器中对应寄存器中的CPOL和CPHA那两位,写0或写1即可。

举例:

此处遇到的C8051F347中的SPI就是一个SPI的controller控制器,即支持软件配置CPOL和CPHA的值,四种模式都支持,此处C8051F347作为SPI从设备,设置了CPOL=1,CPHA=0的模式,因此,此处对应主芯片Blackfin F537中的SPI控制器,作为Master主设备,其SPI的模式也要设置为CPOL=1,CPHA=0。

优缺点

SPI接口具有如下优点:

1) 支持全双工操作;

2) 操作简单;

3) 数据传输速率较高。

同时,它也具有如下缺点:

1) 需要占用主机较多的口线(每个从机都需要一根片选线);

2) 只支持单个主机。